异步十进制加法计数器是在4位异步二进制加法计数器的基础上经过适当修改获得的。它跳过了1010~1111六个状态,利用自然二进制数的前十个状态0000~1001实现十进制计数。 4个JK触发器组成的8421BCD码异步十进制计数器: 1.计数状态顺序表 十进制计数器状态顺序表:

|

计 数

顺 序 |

计 数 器 状 态 |

|

Q3 Q2 Q1 Q0 |

|

0

1

2

3

4

5

6

7

8

9

10 |

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

0 0 0 0 |

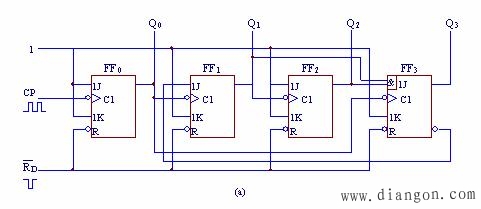

2.逻辑电路图如图(a)所示.

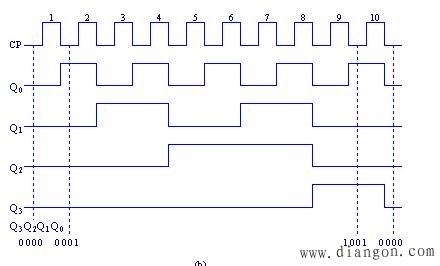

图 8421BCD码异步十进制加法计数器(a)逻辑图(b)波形图

3.工作原理

FF0和FF2为T′触发器。

设计数器从Q3Q2Q1Q0=0000状态开始计数。

这时J1= =1,FF1也为T′触发器。因此,输入前8个计数脉冲时,计数器按异步二进制加法计数规律计数。在输入第7个计数脉冲时,计数器的状态为Q3Q2Q1Q0=0111。这时, J3=Q2Q1=1、 K3=1。 =1,FF1也为T′触发器。因此,输入前8个计数脉冲时,计数器按异步二进制加法计数规律计数。在输入第7个计数脉冲时,计数器的状态为Q3Q2Q1Q0=0111。这时, J3=Q2Q1=1、 K3=1。

输入第8个计数脉冲时,FF0由1状态翻到0状态,Q0输出的负跃变,一方面使FF3由0状态翻到1状态;与此同时,Q0输出的负跃变也使FF1由1状态翻到0状态,FF2也随之翻到0状态。这时计数器的状态为Q3Q2Q1Q0=1000, =0使J1= =0使J1= =0。因此,在Q3=1时,FF1只能保持在0状态,不可能再次翻转。 =0。因此,在Q3=1时,FF1只能保持在0状态,不可能再次翻转。

输入第9个计数脉冲时,计数器的状态为Q3Q2Q1Q0=1001。这时,J3=0、K3=1。

输入第10个计数脉冲时,计数器从1001状态返回到初始的0000状态,电路从而跳过了1010~1111六个状态,实现了十进制计数,同时Q3端输出一个负跃变的进位信号。

4.工作波形。如图(b)所示。 |