|

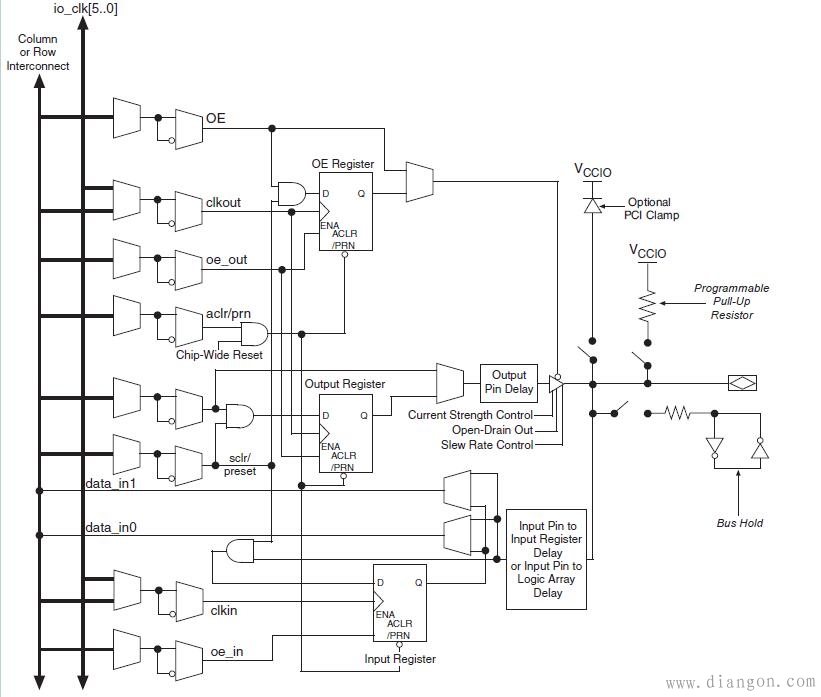

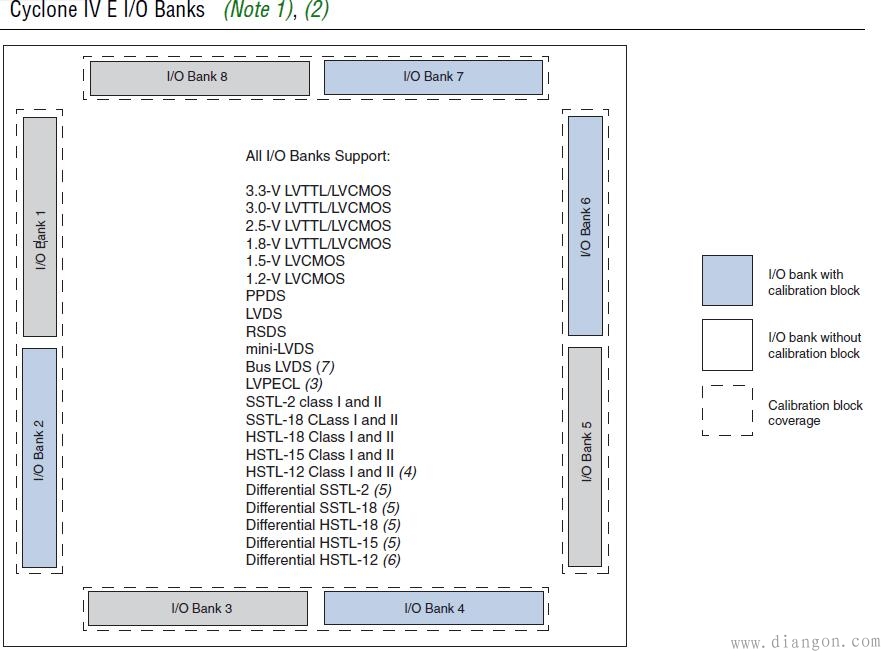

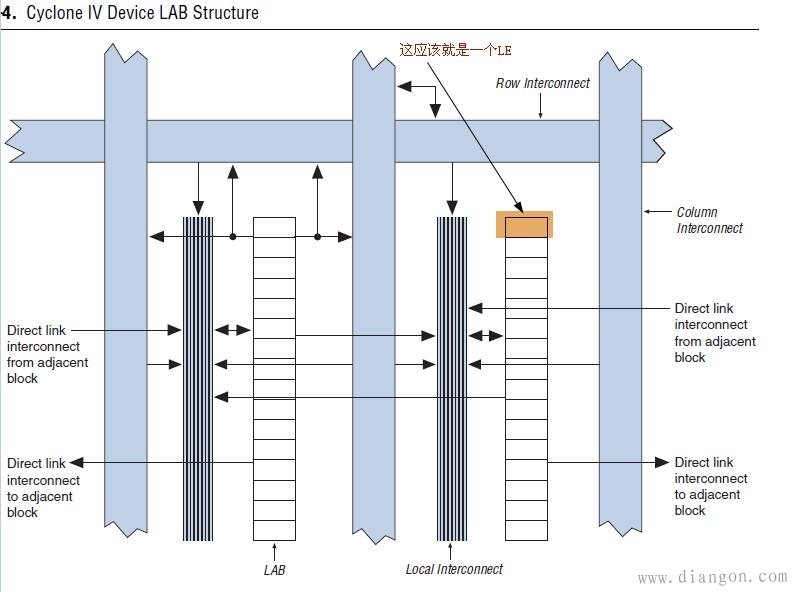

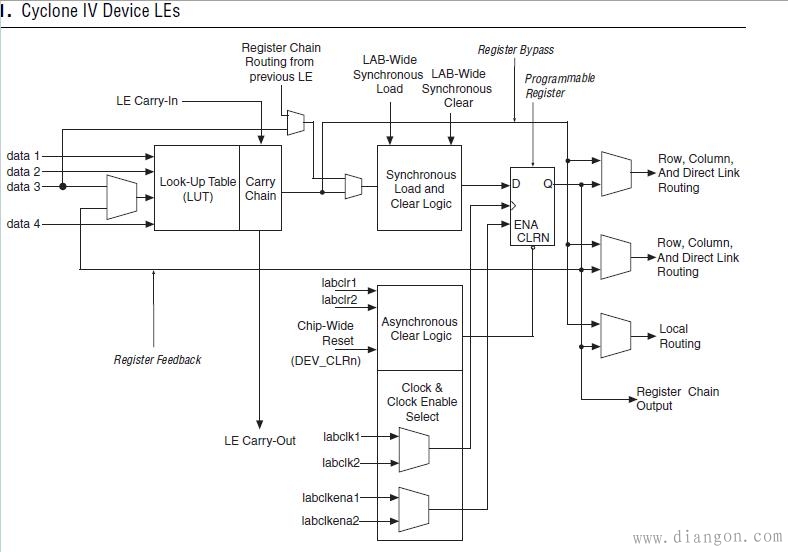

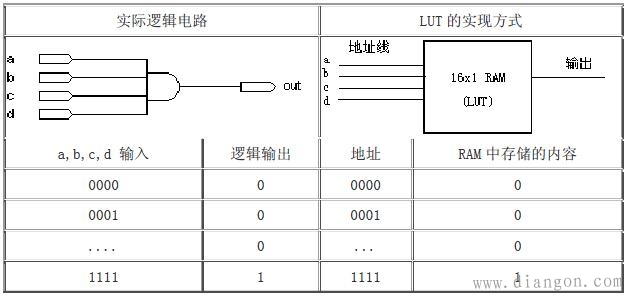

FPGA芯片主要由三部分组成,分别是IOE(input output element,输入输出单元)、LAB(logic array block,逻辑阵列块,对于Xilinx称之为可配置逻辑块CLB)和Interconnect(内部连接线)。 1.IOE IOE是芯片与外部电路的物理接口,主要完成不同电气特性下输入/输出信号的驱动与匹配要求,比如从基本的LVTTL/LVCMOS接口到PCI/LVDS/RSDS甚至各种各样的差分接口,从5V兼容到3.3V/2.5V/1.8V/1.5V的电平接口,下面是ALTERA公司的Cyclone IV EP4CE115F29设备的IOE结构  图1 EP4CE115F29设备的IOE结构图 FPGA的IOE按组分类,每组都能够独立地支持不同的I/O标准,通过软件的灵活配置,可匹配不同的电器标准与IO物理特性,而且可以调整驱动电流的大小,可以改变上/下拉电阻,Cyclone IV设备有8个IO blank(组),见下图:  图2 Cyclone IV设备的IO组 2.LAB LAB是FPGA的基本逻辑单元,其实际的数量和特性依据所采用的器件的不同而不同,EP4CE115F29设备的每个LAB的布局包括16个LE、LAB控制信号、LE carry chains、Register chains和Local interconnect,其LAB结构图如下:  图3 LAB结构图 LE是Cyclone IV设备最小的逻辑单元,每个LE主要有LUT和寄存器组成的,  图4 LE的结构图 查找表LUT(Look-Up-Table)其本质是一个静态存储器SRAM,目前FPGA多采用4输入的LUT,每个LUT可以看作一个有4位地址线的16x1的RAM。当我们通过原理图或HDL语言描述了一个逻辑电路后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。这样,在FPGA工作时,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出。  图5 LUT的实现原理图 3.Interconnect FPGA内部连接线很丰富,根据数据手册的描述,主要有图3中的Row interconnect、column interconnect、Direct link interconnect、和Local interconnect和Register chain interconnect(寄存器之间连接的连接线)。 内部连接线联通FPGA内部的所有单元,而连线的长度和工艺决定着信号再连接线上的驱动能力和传输速度。在实际开发中,设计者不需要直接选择连接线,布局布线器可自动地根据输入逻辑网表(这由综合生成)的拓扑结构和约束条件选择连接线来连通各个逻辑单元,所以,从本质上来说,布线资源的使用方法和设计的结果有密切和直接、直接的关系。 |

电工学习网 ( )

GMT+8, 2023-3-17 19:25