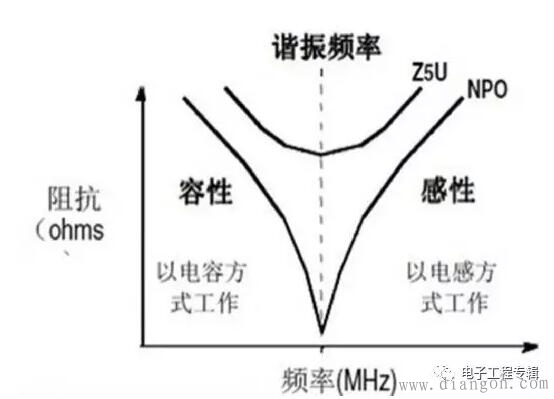

ЁЁЁЁгЩгкКИХЬКЭв§НХЕФдвђЃЌУПИі ЕчШнЖМДцдкЕШаЇДЎСЊЕчИаЃЈESLЃЉЃЌвђДЫздЩэЛсаЮГЩвЛИіДЎСЊаГеёЕчТЗЃЌLCДЎСЊаГеёЕчТЗДцдквЛИіаГеёЦЕТЪЃЌЫцзХ ЕчСІЕФЦЕТЪВЛЭЌЃЌЕчШнЕФЬиадвВЫцжЎБфЛЏЃЌдкЙЄзїЦЕТЪЕЭгкаГеёЦЕТЪЪБЃЌЕчШнзмЬхГЪШнадЃЌдкЙЄзїЦЕТЪИпгкаГеёЦЕТЪЪБЃЌЕчШнзмЬхГЪИаадЃЌДЫЪБШЅёюЕчШнОЭЪЇШЅСЫШЅёюЕФаЇЙћЃЌШчЯТЭМЫљЪОЁЃвђДЫЃЌвЊЬсИпДЎСЊаГеёЦЕТЪЃЌОЭвЊОЁПЩФмНЕЕЭЕчШнЕФЕШаЇДЎСЊЕчИаЁЃ

ЁЁЁЁЕчШнЕФШнжЕбЁдёвЛАуШЁОігкЕчШнЕФаГеёЦЕТЪЁЃ

ЁЁЁЁВЛЭЌЗтзАЕФЕчШнгаВЛЭЌЕФаГеёЦЕТЪЃЌЯТБэСаГіСЫВЛЭЌШнжЕВЛЭЌЗтзАЕФЕчШнЕФаГеёЦЕТЪЃК

ЁЁЁЁашвЊзЂвтЕФЪЧЪ§зжЕчТЗЕФШЅёюЃЌЕЭЕФESRжЕБШаГеёЦЕТЪИќЮЊживЊЃЌвђЮЊЕЭЕФESRжЕПЩвдЬсЙЉИќЕЭзшПЙЕФЕНЕиЭЈТЗЃЌетбљЕБГЌЙ§аГеёЦЕТЪЕФЕчШнГЪЯжИаадЪБШдФмЬсЙЉзуЙЛЕФШЅёюФмСІЁЃ

ЁЁЁЁНЕЕЭШЅёюЕчШнESLЕФЗНЗЈЃК

ЁЁЁЁШЅёюЕчШнЕФESLЪЧгЩгкФкВПСїЖЏЕФЕчСїв§Ц№ЕФЃЌЪЙгУЖрИіШЅёюЕчШнВЂСЊЕФЗНЪНПЩвдНЕЕЭЕчШнЕФESLгАЯьЃЌЖјЧвНЋСНИіШЅёюЕчШнвдЯрЗДзпЯђЗХжУдквЛЦ№ЃЌДгЖјЪЙЫќУЧЕФФкВПЕчСїв§Ц№ЕФДХЭЈСПЯрЛЅЕжЯћЃЌФмНјвЛВННЕЕЭESLЁЃЃЈДЫЗНЗЈЪЪгУгкШЮКЮЪ§ФПЕФШЅёюЕчШнЃЌзЂвтВЛвЊЧжЗИDELLЙЋЫОЕФзЈРћЃЉ

ЁЁЁЁICШЅёюЕчШнЕФЪ§ФПбЁдё

ЁЁЁЁдкЩшМЦдРэЭМЕФЪБКђЃЌОГЃгіЕНЕФЮЪЬтЪЧЮЊаОЦЌЕФЕчдДв§НХЩшМЦШЅёюЕчШнЃЌЩЯУцвбОНщЩмСЫШЅёюЕчШнЕФШнжЕбЁдёЃЌЕЋЪЧЪ§ФПбЁдёдѕУДШЗЖЈФиЃПРэТлЩЯЪЧУПИіЕчдДв§НХзюКУЗжХфвЛИіШЅёюЕчШнЃЌЕЋЪЧдкЪЕМЪЧщПіжаЃЌШДОГЃПДЕНШЅёюЕчШнЕФЪ§ФПвЊЩйгкЕчдДв§НХЪ§ФПЕФЧщПіЃЌШчfreescaleЬсЙЉЕФiMX233ЕФPDKдРэЭМжаЃЌФкДцSDRAMга15ИіЕчдДв§НХЃЌЕЋЪЧШЅёюЕчШнЕФЪ§ФПЪЧ10ИіЁЃ

ЁЁЁЁШЅёюЕчШнЪ§ФПбЁдёвРОнЃК

ЁЁЁЁдкВМОжПеМфдЪаэЕФЧщПіЯТЃЌзюКУзіЕНвЛИіЕчдДв§НХЗжХфвЛИіШЅёюЕчШнЃЌЕЋЪЧдкПеМфВЛзуЕФЪБКђЃЌПЩвдЪЪЕБЯїМѕЕчШнЕФЪ§ФПЃЌОпЬхЧщПігІИУИљОнаОЦЌЩЯЕчдДв§НХЕФОпЬхЗжВМОіЖЈЃЌвђЮЊГЇМвдкЩшМЦICЕФЪБКђЃЌОГЃЪЧМИИіЕчдДв§НХдквЛЦ№ЃЌетбљПЩвдЙВгУШЅёюЕчШнЃЌМѕЩйШЅёюЕчШнЕФЪ§ФПЁЃ

|